用法與探討

用法:

1.有clock的always區塊要使用nonblocking。

2.無clock的always區塊使用blocking。

3.continuous assignment使用blocking。

4.一個always區塊中不能同時使用blocking與nonblocking。

探討:

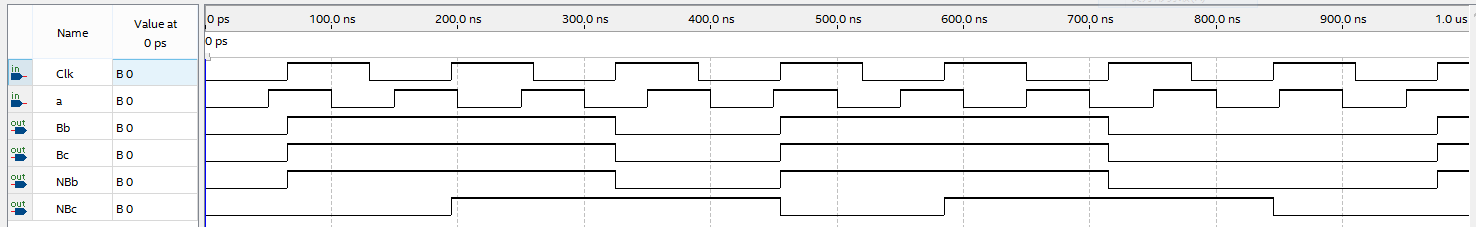

Blocking assignment : 每行程式碼依序執行並完成,因此

B_b = a ; ※ 依序進行(第一步)

B_c = B_b ( = a ) ; ※ 依序進行(第二步)

Nonblocking assignment : 每行程式碼同時執行並完成,因此

NB_b = a、NB_c = NB_b ( 不等於 a,為先前的NB_b ) ※ 同時進行

測試:

module BANB(

input Clk,a,

output reg B_b,B_c,NB_b,NB_c);

always@(posedge Clk) begin

//blocking

B_b = a;

B_c = B_b;

end

always@(posedge Clk) begin

//non-blocking

NB_b <= a;

NB_c <= NB_b;

end

endmodule

結果:

參考資料:

(筆記) 如何使用blocking與nonblocking assignment? (SOC) (Verilog)