各種Always,多個Always

Blocking、Non-Blocking

Always Order

模擬環境:Quartus Prime Lite Edition 16.1.0

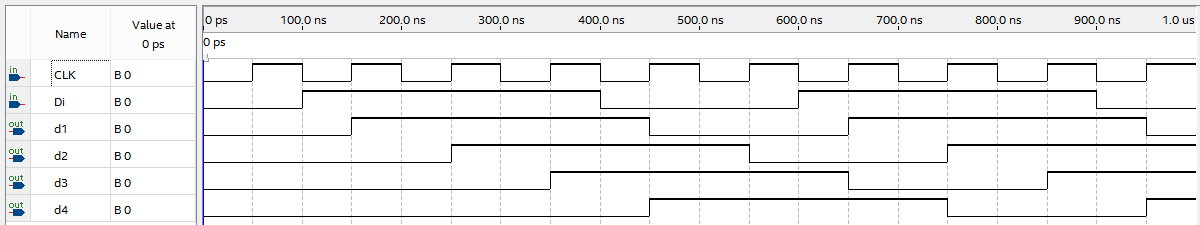

module Always_Order(CLK,Di,d1,d2,d3,d4);

input CLK,Di;

output reg d1,d2,d3,d4;

always @(posedge CLK) d1 = Di;

always @(posedge CLK) d2 = d1;

always @(posedge CLK) d3 = d2;

always @(posedge CLK) d4 = d3;

endmodule

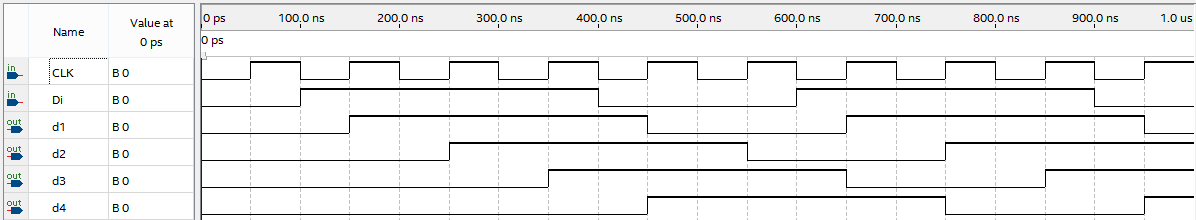

module Always_Order(CLK,Di,d1,d2,d3,d4);

input CLK,Di;

output reg d1,d2,d3,d4;

always @(posedge CLK) d1 <= Di;

always @(posedge CLK) d2 <= d1;

always @(posedge CLK) d3 <= d2;

always @(posedge CLK) d4 <= d3;

endmodule

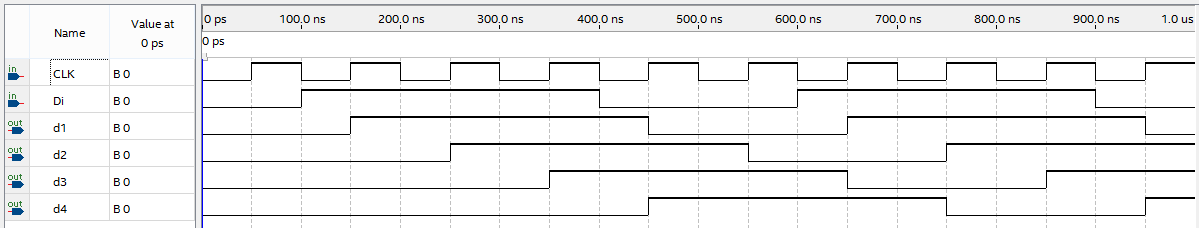

module Always_Order(CLK,Di,d1,d2,d3,d4);

input CLK,Di;

output reg d1,d2,d3,d4;

always @(posedge CLK) begin

d1 = Di;

d2 = d1;

d3 = d2;

d4 = d3;

end

endmodule

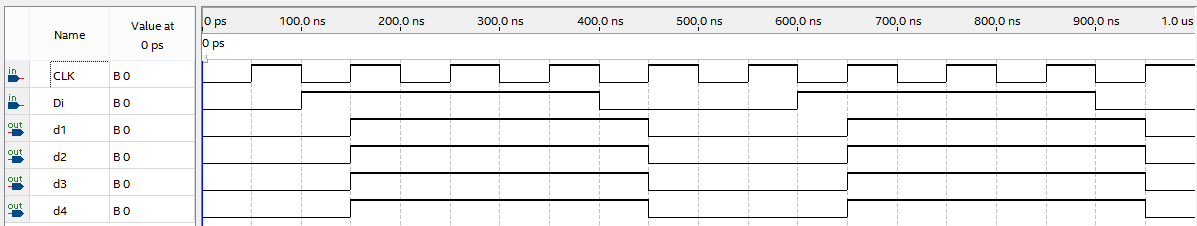

module Always_Order(CLK,Di,d1,d2,d3,d4);

input CLK,Di;

output reg d1,d2,d3,d4;

always @(posedge CLK) begin

d1 <= Di;

d2 <= d1;

d3 <= d2;

d4 <= d3;

end

endmodule